次世代集積回路用メタルゲート材料開発のための新しい設計原理を確立

産官学連携“High-kネット”の大きな成果

2005.11.29

独立行政法人物質・材料研究機構

NIMSの超鉄鋼研究センター 金相グループは、世界一の強度と導電率バランスを持つ銅合金の開発に成功した。

概要

- 独立行政法人物質・材料研究機構 (理事長 : 岸 輝雄) ナノマテリアル研究所 (所長 : 青野 正和) ナノ立体配置グループの知京 豊裕と、筑波大学の白石 賢二、千葉大学の中山 隆史、株式会社 半導体先端テクノロジーズ(Selete)は、広島大学 (宮崎 誠一 教授) 、大阪大学 (渡部 平司 助教授) 、早稲田大学 (山田 啓作 教授、ナノテクノロジー総合支援プロジェクトセンター) らと共同で、金属ゲートとHigh-k膜 (高誘電率ゲート絶縁膜) を用いた極微細CMOSトランジスタの設計に適用できる金属/高誘電体ゲート絶縁膜 (high-k材料) 界面で起きている電子レベルの現象を説明する理論構築に世界ではじめて成功した。

- 現在の集積回路の主流であるMOSFETではSiO2をゲート絶縁膜として使用しているが、トランジスタの小型化が進み、このゲート絶縁膜の厚さが限界に達してきている。そのために、ゲート絶縁膜のリーク電流の問題は集積回路全体の性能を左右するようになり、Siベースの半導体開発に限界がささやかれるようになってきた。

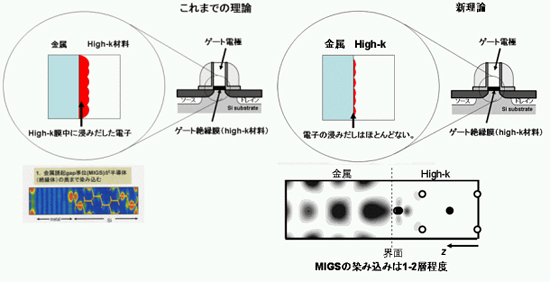

- これをブレークスルーするためにこれまでのSiをベースにしたMOSFET構造に代わり金属/high-k材料を用いる半導体開発が進められてきたが、Siベースの材料開発に用いられてきた設計理論体系が金属/high-k材料では成り立たず、時間のかかる試行錯誤的な研究開発を進めざるを得なかった。

- 今回構築した理論では、金属とhigh-k材料の界面の電子状態を「一般化された電荷中性点」という新しい概念を取り入れることにより、界面の電気特性が大きく変化することを世界ではじめて説明することができたもので、この理論は、最先端のクリーンルームを持つSeleteにおいて並行して行われた実験的検証からも証明された。

- この理論を用いることにより、金属とhigh-k材料との組み合わせにより生じる界面の性質を理論的に予測することが可能になり、今後の集積回路用材料開発に大きな指針になることが期待され、開発が懸念されていたhigh-kメタルゲートを用いたトランジスタの2010年までの実用化にめどが立った。

図2 Cu-24wt%Ag合金の強度と導電率の関係