Siナノデバイスのための画期的な電極形成法を学独連携で実現

Si基板への不純物添加を伴わない画期的な電極形成法を発見

2010.12.08

独立行政法人物質・材料研究機構

国立大学法人千葉大学

国立大学法人東京工業大学

国立大学法人名古屋大学

国立大学法人筑波大学

NIMS 半導体材料センターは、千葉大学、東京工業大学、名古屋大学、筑波大学、早稲田大学、JST-CRESTと共同で将来のナノデバイス実現のための新しい電極形成法を開発した。

概要

- 独立行政法人物質・材料研究機構 (理事長 : 潮田 資勝) 半導体材料センター (センター長 : 知京 豊裕) は、千葉大学、東京工業大学、名古屋大学、筑波大学、早稲田大学、JST-CRESTと共同で将来のナノデバイス実現のための新しい電極形成法を開発した。

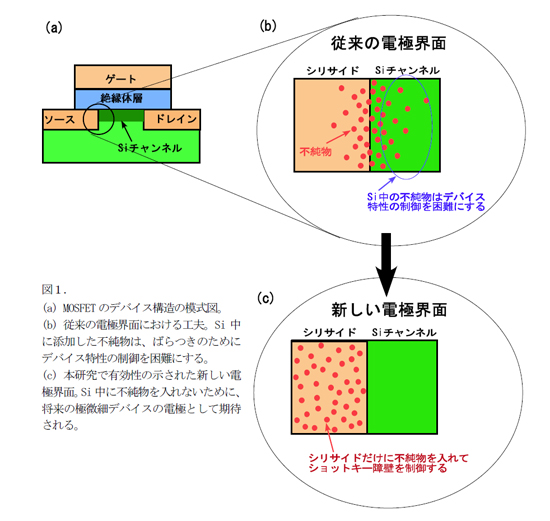

- 今回の開発はSi側には手を加えず、金属側のみに不純物を添加することで、金属/Si界面のショットキー障壁高さを制御できることを千葉大学が理論的に予測し、それを物質・材料研究機構、東京工業大学、名古屋大学、筑波大学、早稲田大学、JST-CRESTが連携する実験で実証したもので、これまでにない全く新しい電極形成法である。

- Si半導体では、接触抵抗値の低い電極/Si接合を実現するために、Si側に不純物を添加することで良好な金属/Si接合を実現してきた。

- しかし、デバイスの微細化とともに、Si側に添加する不純物の位置のばらつきや濃度のばらつきが金属/Si界面に影響しはじめ、安定した電極構造が実現できなくなっていた。

- 今後、Siデバイスの接合領域はますまず微細化し、構造もSi細線を使ったデバイスなど三次元化していく傾向にある。しかし、これまでは安定した電極を形成する手段がなく、接触抵抗も大きいなど課題を抱えていた。今回の成果はこれまでの課題を解決する画期的な方法である。

- 集積回路や将来のナノデバイスではナノ空間における材料の生成過程やその性質を根本的な仕組みから理解することが本質的な問題解決につながる。今回の成果は、様々な専門性を持つ多くの研究者、研究機関が携わることではじめて実証できた成果である。

- 今回の研究成果は、日本時間12月8日 (水) 午後16時45分 (サンフランシスコ現地時間12月7日午前10時45分) に、International Electron Device Meeting(IEDM)2010で発表される。